## OpenFPGA:

## A Complete Open Source Framework for FPGA Prototyping

THE UNIVERSITY OF UTAH

B.Chauviere, A. Alacchi, E. Giacomin, X. Tang and P.-E. Gaillardon University of Utah, ECE Department, Salt Lake City, UT, 84112, USA baudouin.chauviere@utah.edu

Laboratory of NanoIntegrated Systems, University of Utah

### Introduction

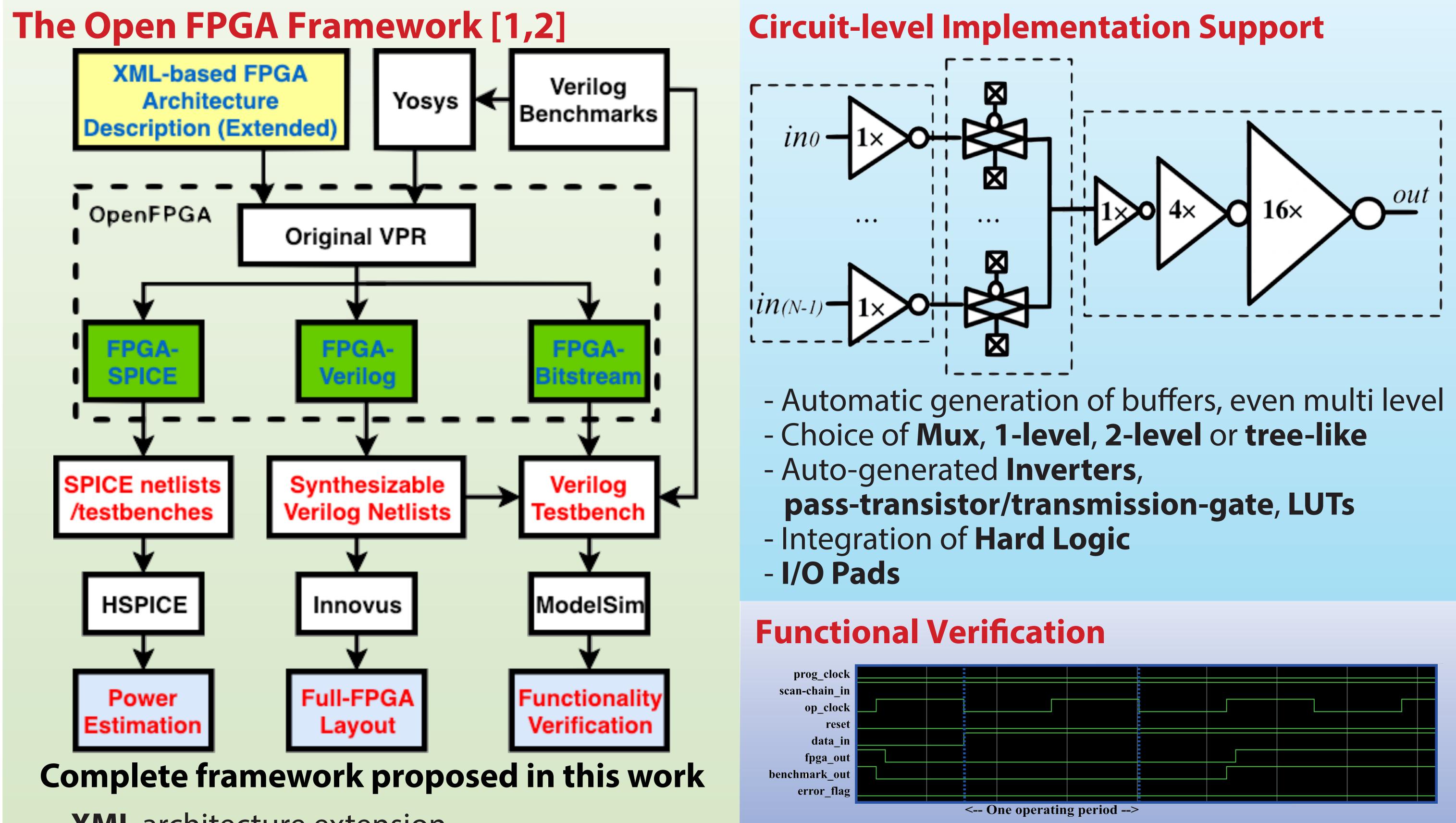

\* FPGA exploration needs more precise and realistic timing analysis, area estimation and power consumption. \* Customizable fabrics show lots of promise for emerging applications \* We propose the first **Open Source framework** allowing **production ready** configurable fabrics with **high customizability**

- XML architecture extension

- Integration of **Yosys**

- 3 outputs, SPICE, Verilog and Bitstream for:

- Golden standard simulations

- Hierarchical Verilog output

- Bitstream generation for benchmarks

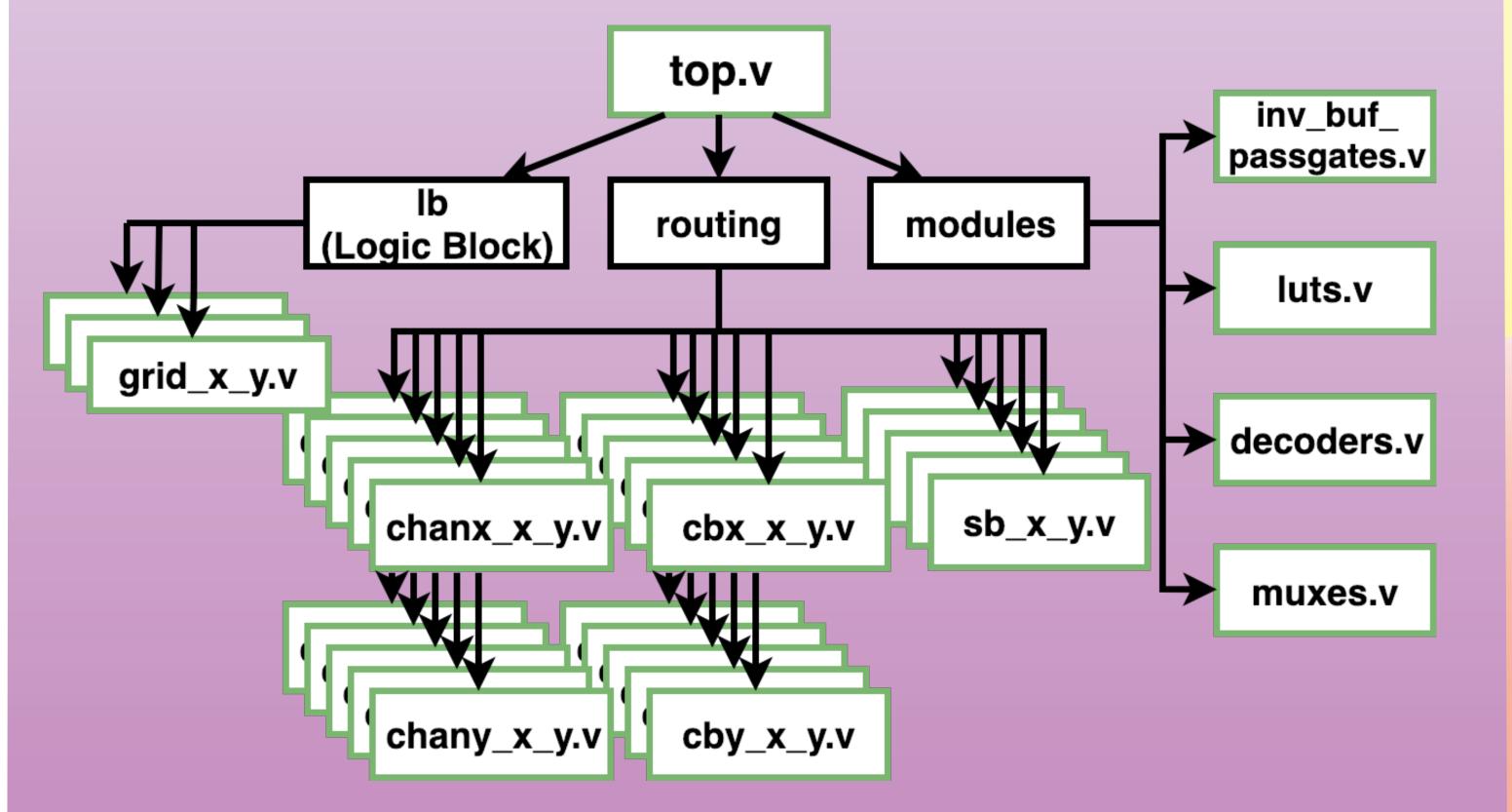

### **Generation of a hierarchical, synthesizable Verilog**

# **Place and Route of a generated**

**20x20 FPGA Fabric**

- Semi-custom design tool: **CADENCE Innovus**

- FPGA characteristics:

- -N = 10

- k = 6- Area: **10.3 mm**<sup>2</sup>

### Conclusion

# Fully-hierarchical generation for easier implementation

- Integration of flexible elements such as **MUXs, transmission-gates or LUTs** - Generation of the Verilog of an homogeneous **FPGA 20x20** ready to be taped-out - Functional verification assuring that the functionnality is correct

**Open Source Design Automation (OSDA) 2019**

March 29, Florence, Italy

**References:** [1] https://github.com/LNIS-Projects/OpenFPGA [2] https://openfpga.readthedocs.io/en/master/

Acknowledgements: DARPA under grant number FA8650-18-2-7855